閃存的讀取中的數據隨機化及其他

上一篇介紹到為了保持閃存的源極電壓為0、或者保證源極電壓在寫入和讀取時不變,NOR和NAND都會有一些設計或者操作上的變化來解決這一問題。在NAND閃存上,另一個比較特殊的需求就是NAND中寫入的數據需要做隨機化處理。這一定程度上也和NAND存儲單元源極電壓的歸一性相關。

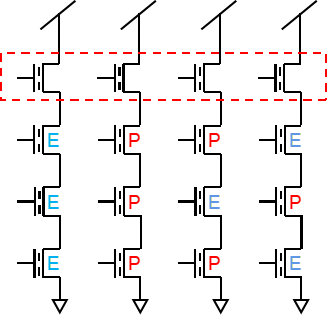

如圖所示,假設有4個NAND串,最下方三行的編程、擦除狀態如下:

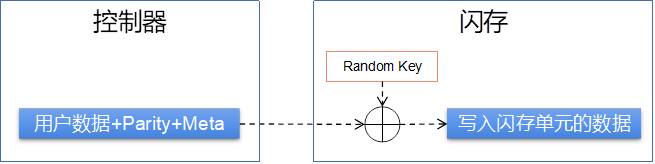

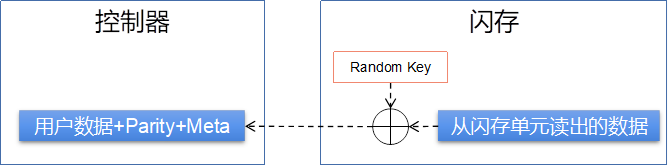

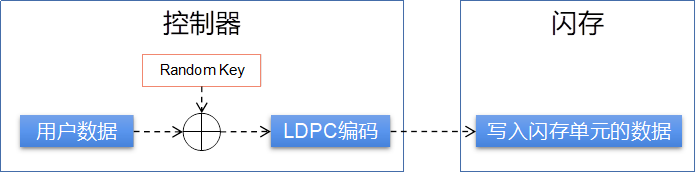

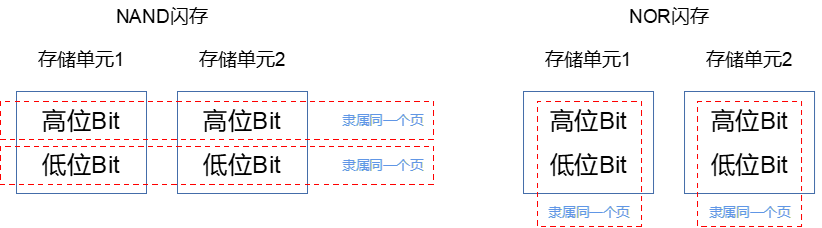

在用戶讀取最上方一行的存儲單元時,這些存儲單元的源極電壓狀態會各不相同,其中第一個串的源極電壓與第二個串的源極電壓之間的差異最大,這和它們下面的存儲單元的編程狀態相關。在遙遠的SLC時代,這一差異尚不足以對數據讀取造成偏差,所以幾乎沒有閃存供應商要求用戶數據做隨機化。但隨著MLC的到來,這一需求就變得十分強烈 -- 哪怕少許的源極電壓歸一化,都會對MLC的性能、可靠性帶來巨大的幫助。因此幾乎所有的NAND閃存廠商都開始要求用戶在存儲單元里均勻地寫入不同編程態的數據。這樣做的好處是,任何一個被讀的閃存單元,決定其源極電壓的其他單元所提供的影響是相同的 (其實對漏端的影響也是如此)。 以MLC為例,由于有E/P1/P2/P3四個狀態,因此NAND閃存廠商希望寫進MLC的數據,這4個狀態能夠各占25%。另外不僅僅占比相同,且位置分布也是均勻的。NAND閃存的塊可以看成是一個二維平面,X軸是頁(page)方向,Y軸是串(String)方向。在這個二維平面上,各個狀態的存儲單元均勻地分布著,且各占25%。TLC也是如此,它和MLC的差異就是在這個平面上有8個不同的編程狀態均勻地分布著,且各占12.5%。 NAND閃存的使用,離不開控制器的支持。當最初幾代需要做數據隨機化處理的NAND閃存面市時,市面上的閃存控制器、尤其是已經大規模量產的閃存控制器還沒有能力支持這種隨機化需求。因此,這幾代NAND閃存,都自帶了內置的Randomizor。這些Randomizor的作用是將控制器寫入閃存的數據先做隨機化處理 -- 實際就是和一些Random Key做異或 -- 再寫入存儲單元。 這些Random Key本身是隨機的,因此哪怕用戶數據不夠隨機,和Random Key異或之后也能得到一個隨機的結果。 在讀出時,閃存需要將存儲單元里的數據和這些Random Key再做一次異或,就能得到原始數據。 但閃存內置的Randomizor也造成了不少壞處,比如: 1) 閃存的讀寫延遲變長了。尤其對讀來說,幾個微秒的Randomization延遲,對性能傷害頗大。 2) 控制器如果不知道閃存內部的Random Key的具體數值,就不會知道寫入閃存的數據究竟應該落在哪個Vt分布上。這對使用BCH編碼做誤碼糾錯的NAND閃存而言,還可以忍受。但對LDPC,或其他依賴閃存Vt做DSP的控制器來說,則不能接受。 因此在最初幾代NAND閃存內置Randomizor之后,所有的NAND都要求控制器具有Randomization的能力 -- 控制器對用戶數據先做隨機化處理,再做LDPC編碼,之后寫入NAND閃存。 讀取就是將這個過程反過來,不多贅述。 當然因為Random Key和閃存的物理結構相關,因此每家NAND閃存供應商還是會提供一組合適的Random Key,給到與他們合作的控制器廠商。控制器廠商所需要做的事情就是讓他們的控制器設計得足夠靈活,以匹配不同NAND原廠的不同代際的產品。 閃存數據隨機化還有其他很多好處,等將來有機會在再作討論。 說了很多閃存源極電壓在讀取時如何保持穩定。由于閃存單元是一個四端器件,因此另外三端:漏極、柵極和襯底,在讀的時候一樣要保持穩定。 用NOR閃存的柵極作一個例子:它的穩定不在于柵極電壓本身的穩定度,而在于柵極電壓多快能夠達到穩定的狀態。NOR閃存的柵極(Word Line,字線)一般是多晶硅,其電阻率比3D NAND閃存的金屬字線要大很多。且由于NOR閃存的讀取延時(tR)很短,一般在100納秒以內,因此要求NOR閃存的柵極電壓能夠在小幾十納秒之內就能達到穩定的狀態。這對于SLC的NOR閃存而言問題不大。但對于MLC NOR閃存則相對困難。和NAND閃存不同,NAND閃存一個存儲單元里面的不同bit隸屬于不同的頁(參見“閃存閾值電壓(Vt)的編碼與用戶數據的對應”),但NOR閃存因其編程是熱電子效應,每個存儲單元的編程功耗太大,所以為了一次存儲更多數據,MLC NOR閃存的存儲單元里的兩個存儲單元隸屬于同一個頁。 因此MLC NAND的數據最多需要通過兩次Vt比較得出(參見“閃存閾值電壓(Vt)的編碼”),而MLC NOR的數據則每回讀出都要比較三次Vt。所以MLC NOR對柵極電壓爬升速度的要求非常高。曾經有一些NOR閃存利用額外的金屬層,在金屬層和柵極字線之間打孔連接,以降低多晶硅柵極的RC值,達到提升tR性能的目的。